Binary Coded Decimal format is a binary encoding of decimal numbers that represents each decimal digit by a fixed binary number. For example, 42 is represented in BCD format by the binary representations of 4 and 2, as shown above. The BCD format is common in electronic systems where numeric digits are displayed, as well as in systems where the rounding and conversion errors introduced by binary floating point representation and arithmetic are undesirable.

We will focus on designing a conversion circuit that converts a BCD formatted number to to a binary formatted number. I chose to detail this direction of conversion as binary to BCD conversion circuits are easily be found by a quick web search.

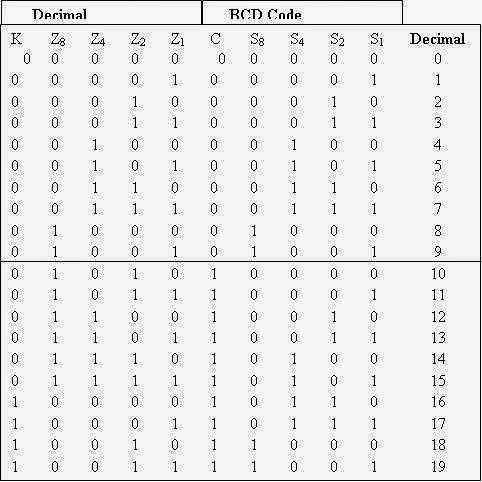

The BCD stands for Binary Coded Decimal Number. In BCD code, each digit of the decimal number is represented as its equivalent binary number. So, the LSB and MSB of the decimal numbers are represented as its binary numbers. There are the following steps to convert the binary number to BCD: First, we will convert the binary number into decimal.

We will consider two algorithms to perform the conversion, the first being a direct arithmetic approach, and the second an iterative algorithm using a finite state machine with data path (FSMD).

We will be designing for the Basys 2 FPGA board which has 8 input switches. We can use the 8 input switches to encode 2 BCD numbers of 4 bits each. We will therefore concern ourselves with designing a circuit to convert a 2 digit BCD number to a 7 bit binary representation (27 = 128 > 99, the largest 2 digit BCD number we can input).

- About Press Copyright Contact us Creators Advertise Developers Terms Privacy Policy & Safety How YouTube works Test new features Press Copyright Contact us Creators.

- In computer science, the double dabble algorithm is used to convert binary numbers into binary-coded decimal (BCD) notation. It is also known as the shift-and-add -3 algorithm, and can be implemented using a small number of gates in computer hardware, but at the expense of high latency.

The first algorithm will simply take the “tens” BCD digit, multiply it by 10, and add the “ones” digit to it. For the conversion of BCD 42, 4 is multiplied by 10, and 2 is added to it, giving us 101010, which is the binary representation of 42. Vcds 18.9.1 loader.

The inputs are 4-bit bcd1 and bcd0, with the output being the converted 7-bit binary representation, bin. We simply multiply bcd1 by 10, add to it a 7-bit adjusted bcd0, and assign it to the output.

To test the circuit, we can route the binary output to a binary to hexadecimal 7-segment multiplexing circuit, which was detailed in my “Stopwatch with the Basys 2 FPGA” blog.

While not a complete testbench, below are a couple of the tested outputs.

From the input switches we can see that BCD 0100 0010, or 42, gives us 2A in hex, which is decimal 42.

Testing the upper limit, BCD 1001 1001, or 99, gives an output of hex 63, which is decimal 99.

Next we will consider an iterative algorithm that will also convert our 2 BCD digits to a 7-bit binary representation. We will have two 4-bit registers for bcd1 and bcd0, as well as a 7-bit binary answer register, bin.

The algorithm is as follows:

- Right shift bcd1, with the LSB shifting to the MSB of bcd0.

- Right shift bcd0, with the LSB shifting to the MSB of bin.

- If bcd0 is now > 4, subtract 3

- repeat steps 1-3, 7 times.

Binary To Bcd Verilog

Lets illustrate this with the example of converting BCD 42, 0100 0010, to binary 42, 0101010.

To implement this algorithm we will use a FSM with data path to control the overall operation of the circuit. When in the idle state and a start signal is asserted, the state will change to operate, in which the FSM will iterate through the 7 bits like the algorithm shown above. Once the algorithm completes, the state will change to done, which will assert a done_tick, and then go back to idle.

Binary To Bcd Converter Verilog

Lets look at the code implementation in chunks.

We define our symbolic states for the FSM operation to be idle, op for operation, and done. The internal signals are declared for registers and their next state logic, for the state (state), converted binary value (bin), iteration variable (n), and BCD inputs (bcd1 & bcd0).

Above we implement the state and data registers, resetting them when reset is asserted, and assigning their next-state logic values at each positive clock edge.

The FSMD next-state logic determines what happens in each state and how a state transition occurs. Assignments before the case statement are defaults that are only changed if overwritten in the case statements. For example, done_tick is normally 0, unless the FSM is in the done state, in which it is set to 1.

In the idle state, the ready line is asserted, and if the start input is asserted, the next state will transition to op, and n_reg is set to 7, the number of iterations.

In the op state the iterative algorithm is achieved by right shifting in the LSB of bcd0 to bin, right shifting in 0 to bcd1, right shifting in the LSB of bcd1 into bcd0, checking if bcd0 is greater than 4, and if so subtracting 3. This happens 7 times until n_reg = 0, in which the state transitions to done.

In the done state, a done_tick line is asserted, letting a possible dependent system know the operation has completed, then the state transitions back to idle.

The final converted binary value in bin_reg is assigned to the output line, bin.

Since the FSMD iterative algorithm requires a finite time to compute, our test circuit has a master FSM that will idle until the start line is asserted, perform a conversion, receive a done tick, and go back to idling. Jhoom barabar jhoom full movie download 480p. Videogames artbooks pdf.

We can see that unlike before where the result was always routed to the output display, we now have to enable the start line to compute the conversion. The intermediate state showing “88” occurs only when the button is pressed and the master FSM rapidly cycles through its states, until it is disengaged. This could be remedied by instead implementing a positive edge detection circuit for the start button input signal.

A binary to binary-coded decimal, or BCD for short, is a method storing decimal numbers in binary form. The majority of the time a number in a logic design is stored as a binary number internally as to simplify math and logic operations and converted to a set of BCD numbers only when it needs to then be sent to something that requires it in decimal number form i.e. a display of some sort. The Verilog and VHDL code below is for an 8-bit binary to BCD decoder that gives and ones, tens and hundreds decimal place output for driving a display or other device.

Binary To Bcd Conversion Verilog

The modules below take a 8-bit binary number on the number input and converts that number into three 4-bit BCD numbers, one for each decimal place. These 4-bit BCD numbers are still binary numbers but each one only goes from 0 to 9, even though 4-bits can go from 0 to 15, to represent the 10 possibilities of a decimal number.